フィボナッチ数列F(n)は,1,1,2,3,5,8.13,21,34,.....のような数列です.

F(n)=F(n-1)+F(n-2) と再帰的に定義されます.

この数列は,いろいろな所に現れます.得られた数列が,フィボナッチ数列であることを証明するには数学的帰納法を用います.

今回は,その典型的な例として,抵抗ラダー回路を取り上げましょう.

■抵抗ラダー回路

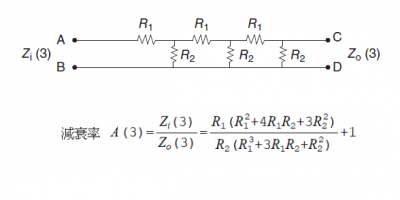

ラダーとは梯子のことで,梯子型に抵抗を並べた回路を,抵抗ラダー回路といいます.例えば,表紙の図は3段のラダー回路です.

A-Bの端子(入力側)から見たインピーダンスをZ_i,

C-Dの端子(出力側)から見たインピーダンスをZ_oとします.

この3段のラダー回路は,A-B側(入力側)にR1の抵抗があるが,C-D側(出力側)にはないので,左右対称ではありません.入力側から見たインピーダンスと出力側から見たインピーダンスの比から,減衰率Z_i/Z_o≡Aが定義されますが,A>1なのでこの回路はアッテネータ(減衰器)として使えます.

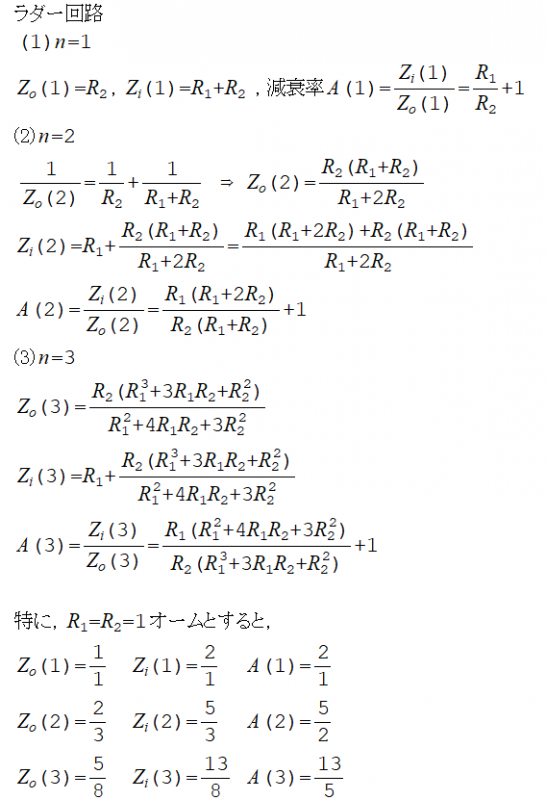

抵抗値をすべて同じR1=R2=1とすると,

ラダーの段数mを増やしていくと,減衰率A(m)=F(2m+1)/F(2m-1)は,2/1,5/2,13/5,34/13,...とフィボナッチ数列が出てきます.

(参考)n=1から3までの計算は以下にありますのでご覧ください.

証明は数学的帰納法を使う練習になりますので,各自試みてください.

■ラダー回路の応用例

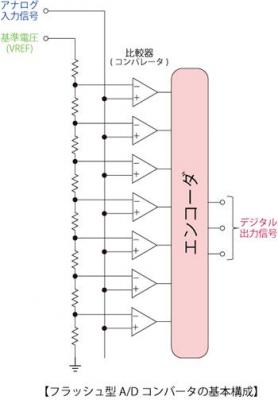

ラダー回路は,アナログ信号が入力されたときに,そのアナログ信号の大きさを,瞬時に8水準に分類する(8ビットのデジタル化)回路(これを8ビットのAD変換といいます)に使われたりもします.次の図をご覧ください.

コンパレータが7個並列に並んでいますね(カスケード結合).

入力信号の大きさを8水準に分類するのは,7個のコンパレータの働きで,

その境界値となる7段階の基準電位をそれぞれに供給します.

この7つの基準電位を発生するのが,一番左の直列に並んだ抵抗ラダー回路です.nビットのAD変換には(2^n)-1個のコンパレータと基準電位がいります.